ASIC Digital Design, Staff Engineer

Category: Engineering

Hire Type: Employee

Job ID 50910BR Date posted 06/24/2024

Our Silicon IP business is all about integrating more capabilities into an SoC—faster. We offer the world’s broadest portfolio of silicon IP—predesigned blocks of logic, memory, interfaces, analog, security, and embedded processors. All to help customers integrate more capabilities. Meet unique performance, power, and size requirements of their target applications. And get differentiated products to market quickly with reduced risk.

At Synopsys, we’re at the heart of the innovations that change the way we work and play. Self-driving cars. Artificial Intelligence. The cloud. 5G. The Internet of Things. These breakthroughs are ushering in the Era of Smart Everything. And we’re powering it all with the world’s most advanced technologies for chip design and software security. If you share our passion for innovation, we want to meet you.

Staff Digital IP Design Engineer

Seeking a highly motivated and innovative Staff digital design engineer with knowledge of DDR and wide-spectrum knowledge of generic IP design methodology.

The candidate would be working as part of a highly experienced DDR controller design and verification team, targeting the current and next generation DDR technology, such as DDR5, LPDDR5. Solid theoretical and practical background in AXI, CHI, CRYPTO and RAS is a solid plus.

The position offers an excellent opportunity to work with a professional team of digital engineers responsible for delivering high-end designs from specification development to performing functional design, performance tests down to successful IP releases.

The controller IP development is very dynamic and provides an endless list of challenges. This work is very challenging, not only given the constant technological changes but also given the ownership and the need to charter unknown waters.

Does this sound like a good role for you?

Key Qualifications

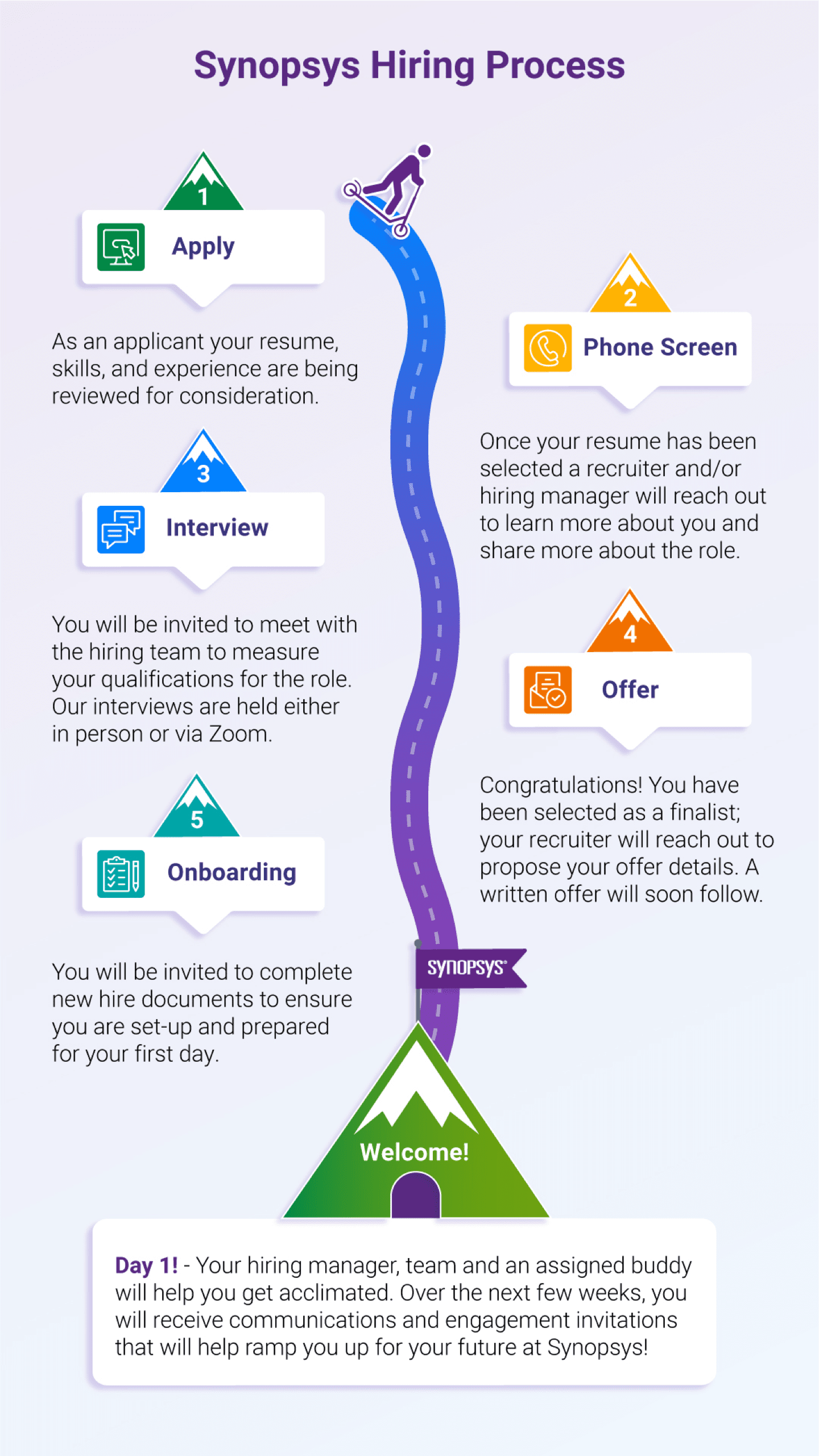

Apply Now

At Synopsys, we’re at the heart of the innovations that change the way we work and play. Self-driving cars. Artificial Intelligence. The cloud. 5G. The Internet of Things. These breakthroughs are ushering in the Era of Smart Everything. And we’re powering it all with the world’s most advanced technologies for chip design and software security. If you share our passion for innovation, we want to meet you.

Staff Digital IP Design Engineer

Seeking a highly motivated and innovative Staff digital design engineer with knowledge of DDR and wide-spectrum knowledge of generic IP design methodology.

The candidate would be working as part of a highly experienced DDR controller design and verification team, targeting the current and next generation DDR technology, such as DDR5, LPDDR5. Solid theoretical and practical background in AXI, CHI, CRYPTO and RAS is a solid plus.

The position offers an excellent opportunity to work with a professional team of digital engineers responsible for delivering high-end designs from specification development to performing functional design, performance tests down to successful IP releases.

The controller IP development is very dynamic and provides an endless list of challenges. This work is very challenging, not only given the constant technological changes but also given the ownership and the need to charter unknown waters.

Does this sound like a good role for you?

Key Qualifications

- MSEE plus a minimum of 8 years of digital design experience in the industry

- Study standard specifications published by JEDEC, define micro architecture at block level based on IP architecture

- Work on micro architecture definition

- work on RTL design based on predefined coding style, SVA is also included, clean RTL check violations in lint, CDC, DFT and synthesis

- Work with verification team to debug and fix RTL issues

- Good knowledge of back-end synthesis tools DC/PT is required

- Must be self-motivated, proactive, and able to balance good design quality while meeting tight deadlines

- May guide more junior peers with aspects of their job. Networks with senior internal and external personnel in own area of expertise

- Good communication skills for interacting between different design groups and customer support teams are required

- Has strong desire to learn and explore new technologies

- Demonstrates good analysis and problem-solving skills

- Knowledge in DDR and interface technologies such as DDR, PCIe is a plus

- Knowledge in AMBA protocols is a plus

- good experience is co-working with UVM-based verification is a plus

- Scripting experience in Shell, Perl, Python and TCL is a plus

- Interacting with Application Engineers for customer support.

Relevant Jobs

-

Test & Validation Engineer

Mississauga, Canada

Engineering

Mississauga, Canada

Engineering

-

Applications Engineering, Sr Staff Engineer

Bengaluru, India

Engineering

Bengaluru, India

Engineering

-

R&D Engineering, Architect

Bengaluru, India, Hyderabad, India, Noida, India

Engineering

Bengaluru, India, Hyderabad, India, Noida, India

Engineering

Available Opportunities

Find the open role that’s right for you.

-

Test & Validation Engineer

Mississauga, Canada

Engineering

Mississauga, Canada

Engineering

-

Applications Engineering, Sr Staff Engineer

Bengaluru, India

Engineering

Bengaluru, India

Engineering

-

R&D Engineering, Architect

Bengaluru, India, Hyderabad, India, Noida, India

Engineering

Bengaluru, India, Hyderabad, India, Noida, India

Engineering

-

Gnu Toolchain Developer

Eindhoven, Netherlands, Porto, Portugal

Engineering

Eindhoven, Netherlands, Porto, Portugal

Engineering

View all job opportunities here

View all job opportunities here