ASIC Digital Design, Principal Engineer

Category: Engineering

Hire Type: Employee

Job ID 6460

Date posted 10/08/2024

| Job Description The candidate will be part of the DesignWare IP Verification R&D team at Synopsys. Person will be expected to specify, design/architect and implement state-of-the-art Verification environments for the DesignWare family of synthesizable cores and perform Verification tasks for the IP cores. Person will work closely with RTL designers and be part of a global team of professional Verification Engineers. Will be working on the next generation connectivity protocols for Commercial, Enterprise and Automotive applications Job role will have a combination of Test planning, Test environment coding both at unit level and system level, Test case coding, debugging, FC coding and testing, meeting quality metric goals and regression management. Requirements: Must have BSEE in EE with 12+ years of relevant experience or MSEE with 10+ years of relevant experience in the following areas:

|

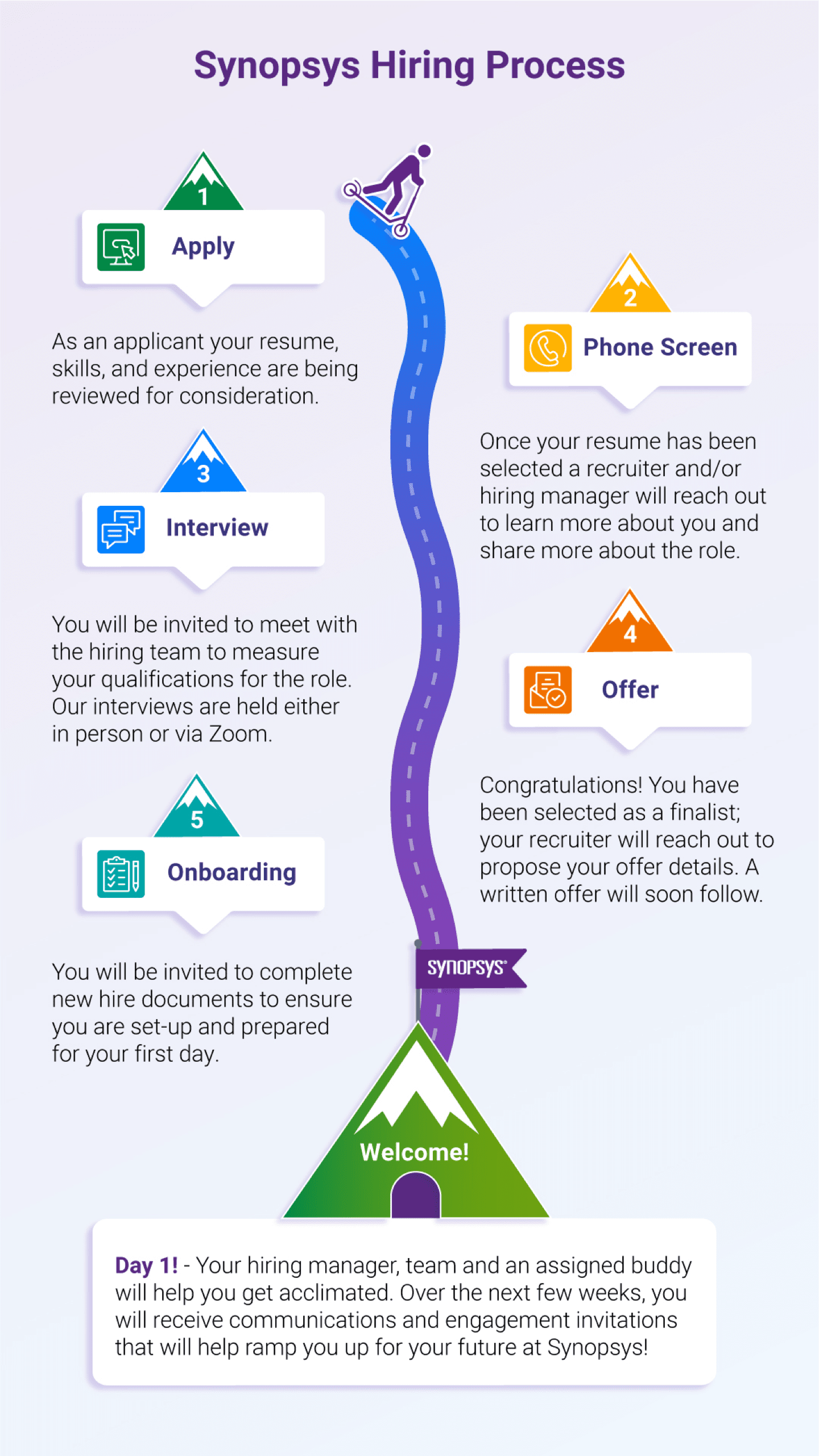

Inclusion and Diversity are important to us. Synopsys considers all applicants for employment without regard to race, color, religion, national origin, gender, sexual orientation, gender identity, age, military veteran status, or disability.

Apply NowRelevant Jobs

-

R&D Architect

Ottawa, Canada

Engineering

-

Principal Solutions Engineer

Sunnyvale, California

Engineering

-

Hardware Principal Engineer

Rungis, France

Engineering

BROWSE JOBS

Find the open role that’s

Find the open role that’s

right for you

-

R&D Architect

Ottawa, Canada

Engineering

-

Principal Solutions Engineer

Sunnyvale, California

Engineering

-

Hardware Principal Engineer

Rungis, France

Engineering

-

R&D Engineer, Formality-6482

Hillsboro, Oregon

Engineering

View all job opportunities here

View all job opportunities here