Synopsys

CULTURE

A community you can

A community you can

be a part of

Learn about life at Synopsys from those who live it.

CULTURE

A community you can

A community you can

be a part of

Learn about life at Synopsys from those who live it.

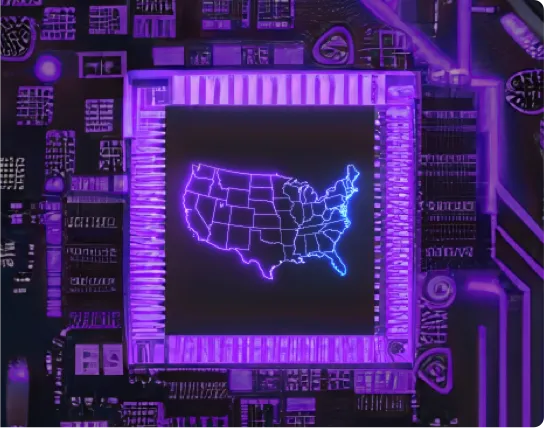

CAREER AREAS

Your best work starts here

BROWSE JOBS

Find the open role that’s

Find the open role that’s

right for you

-

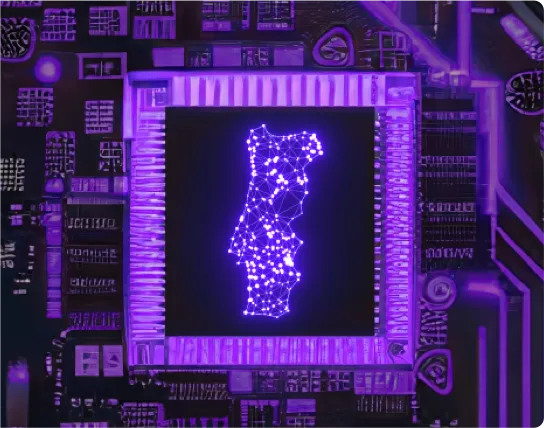

R&D Project and Technology Enabler

Porto Salvo, Portugal

-

ASIC Digital Design, Senior Engineer

Moreira, Portugal

-

ASIC Digital Design Engineer, Senior Staff

Dublin, Ireland

-

ASIC Digital Verification Engineer

Moreira, Portugal

View all job opportunities here

View all job opportunities here

Awards

We're proud to receive several

We're proud to receive several

recognitions

Explore the Possibilities

with Synopsys

Follow #lifeatSynopsys